Map & Guide v9.0 German serial key or number

Map & Guide v9.0 German serial key or number

Maps

What is your source data?

All of our data sources are detailed here: https://www.mapbox.com/about/maps/#data-sources

What languages do you support?

All Mapbox template maps use the Mapbox Streets vector tileset for map features. In this tileset, there are different name fields for each of the label layers. Mapbox Streets supports the name field (the name or names used locally for the place) globally and thus Mapbox maps have partial language coverage for over 100 local languages and we continue to add to these over time. View the complete list of languages we fully support.

Can I upload my own data?

Yes, you can upload both Datasets and Tilesets. Datasets provide access to feature geometries (points, lines, and polygons) and properties (attributes), both of which can be edited in the Mapbox Studio dataset editor or through the Mapbox Datasets API.

Tilesets are lightweight collections of vector data that are optimized for rendering and are not editable, but can be styled in the Mapbox Studio style editor. View our help guides to see accepted file types and transfer limits.

Can I store Mapbox maps data permanently?

You may temporarily cache maps on end-user devices (e.g., laptops, smartphones, or tablets) for offline use, but each device must populate its cache using direct requests to the Maps APIs and content from a cache may only be consumed by a single end user. On mobile devices, you may only cache up to the limits set in the applicable Mapbox SDK, and you may not circumvent or change those limits. You may not redistribute maps, including from a cache, by proxying, or by using a screenshot or other static image instead of accessing maps through the Maps APIs. You may not scrape or download maps for any purpose other than temporary offline caching on a single end user’s device.

Can I trace or create my own data using your tools?

You may use Studio or third-party software to trace Mapbox Satellite Imagery and produce derivative vector datasets, but only for non-commercial purposes and for OpenStreetMap. If you would like to use Studio to trace Mapbox Satellite Imagery for commercial purposes, contact us.

Intel Quartus Prime Pro Edition User Guide: Programmer

| Updated for: |

|---|

| Intel® Quartus® Prime Design Suite 19.4 |

Follow these steps to generate primary device programming files:

- To specify programming options that enable features in the primary device programming file, such as Configuration, Error Detection CRC, and device Security options, click Assignments > Device > Device & Pin Options. Device & Pin Options Dialog Box describes all options.1Figure 2. Device & Pin Options Dialog Box ( Intel® Stratix® 10 Design)

- To generate primary device programming files, click Processing > Start > Start Assembler, or double-click Assembler on the Compilation Dashboard. The Assembler generates the programming files according to the options you specify.

- After running the Assembler, view detailed information about programming file generation, including the programming file Summary and Encrypted IP information in the Assembler report folder in the Compilation Report. Figure 3. Assembler ReportsNote: Each successive release of the Intel® Quartus® Prime software typically includes:

- Added support for new features in supported FPGA devices.

- Added support for new devices.

- Efficiency and performance improvements.

- Improvements to compilation time and resource use of the design software.

You can use the Programming File Generator or Convert Programming Files dialog box to generate secondary programming files:

- The Programming File Generator supports advanced programming features and is optimized for Intel® Agilex™ , Intel® Stratix® 10, Intel® MAX® 10, and Intel® Cyclone® 10 LP devices.

- The Convert Programming Files dialog box supports all devices released prior to Intel® Stratix® 10 devices.

| Programming File Generator | Convert Programming Files | ||

|---|---|---|---|

| Device Support |

|

| APEX20K, Arria® II GX and GZ, Arria® V, Cyclone®, Cyclone® II, Cyclone® III and LS, Cyclone® IV E and GX, Cyclone® V, HardCopy® III, HardCopy® II, HardCopy® IV, MAX® V, Stratix®, Stratix® II, Stratix® III, Stratix® IV, Stratix® V |

- Generate the primary programming files for your design, as Generating Primary Device Programming Files describes.

- Click File > Programming File Generator.

- For Device family, select your target device. The options available in the Programming File Generator change dynamically, according to your device and configuration mode selection.

- For Configuration mode, select an Active Serial mode that your device supports. Configuration Modes (Programming File Generator) describes all modes.

- On the Output Files tab, enable the checkbox for generation of the file you want to generate. The Input Files tab is now available. Secondary Programming Files (Programming File Generator) describes all output files.

- Specify the Output directory and Name for the file you generate. Output Files Tab Settings (Programming File Generator) describes all options.Figure 4. Programming File Generator

- To specify a .sof file that contains the configuration bitstream data, on the Input Files tab, click Add Bitstream. To include raw data, click Add Raw Data and specify a Hexadecimal (Intel-Format) File (.hex) or Binary (.bin) file.

- To specify bitstream authentication or encryption security settings for the file, select the .sof and click Properties, as Enabling Bitstream Authentication (Programming File Generator) describes.2Figure 5. Input Files Tab

- To specify the .sof file that occupies the flash memory partition, click Add Partition on the Configuration Device tab. Add Partition Dialog Box (Programming File Generator) describes all options.Figure 6. Add Flash Partition

- To select a supported flash memory device and predefined programming flow, click Add Device on the Configuration Device tab. Alternatively, click <<new device>> to define a new flash memory device and programming flow. Configuration Device Tab Settings describes all settings.

- Click the Select button for Flash Loader and select the device that controls loading of the flash memory device. Select Devices (Flash Loader) Dialog Box describes all settings.

- After you specify all options in Programming File Generator, the Generate button enables. Click Generate to create the files.

| Programming Mode | Description | Supports Devices |

|---|---|---|

| Active Serial x4 | For storing configuration data in a low-cost serial configuration device with non-volatile memory and four-pin interface. Serial configuration devices provide a serial interface to access the configuration data. During device configuration, Intel® Stratix® 10 devices read the configuration data through the serial interface, decompress the data if necessary, and configure their SRAM cells. |

|

| AVST x8 | The Avalon®-ST configuration mode uses an external host, such as a microprocessor or Intel® MAX® 10 device. The external host controls the transfer of configuration data from an external storage such as flash memory to the FPGA. The design that controls the configuration process resides in the external host. You can use the PFL II IP core with an Intel® MAX® 10 device as the host to read configuration data from a flash memory device that configures an Intel® Stratix® 10 FPGA. | |

| AVST x16 | ||

| AVST x32 | ||

| 1-Bit Passive Serial | An external controller passes configuration data to one or more FPGA devices via a serial data stream. The FPGA device is a slave device with a 5-wire interface to the external controller. The external controller can be an intelligent host such as a microcontroller or CPU. | Intel® Cyclone® 10 LP |

| Active Serial | Stores configuration data in a low-cost serial configuration device with non-volatile memory and four-pin interface. | |

| Internal Configuration | Uses a .pof file for internal configuration of the Intel® MAX® 10 device’s Configuration Flash Memory (CFM) and User Flash Memory (UFM) via a download cable Intel® Quartus® Prime Programmer. | Intel® MAX® 10 |

| Programming File Type | Extension | Description |

|---|---|---|

| Hexadecimal ( Intel®-Format) Output File for SRAM | .hexout | An ASCII text file in Intel® hexadecimal format that contains configuration data for programming a parallel data source, such as a configuration device or a mass storage device. The parallel data source in turn configures an SRAM-based Intel device. |

| JTAG Indirect Configuration File | .jic | Proprietary Intel® FPGA file type that stores serial flash programming data for programming via Intel® FPGA JTAG pins. This method only supports Active Serial configuration. Before programming the flash, the Programmer first configures the FPGA with the Serial Flash Helper Design. |

| Map File | .map | A text file containing the byte addresses of pages and data stored in the memory of a configuration device for |

| Programmer Object File | .pof | A binary file used by the Programmer to program a flash memory device via active serial header, or to program a flash memory device via the Parallel Flash Loader Intel FPGA IP. |

| Raw Binary File | .rbf | Configuration bitstream file for use with a third-party data source, partial reconfiguration, or HPS data source. Supports Passive Serial (PS) and Avalon®-Streaming (AVST) modes. |

| Raw Binary File for CvP Core Configuration | .rbf | A binary file that containing logic that is programmed by configuration (CRAM) for CvP phase 2. The core bitstream is in .rbf format. |

| Raw Binary File for HPS Core Configuration | A binary file that containing logic that is programmed by configuration (CRAM) for HPS configuration phase 2. The core bitstream is in .rbf format. | |

| Raw Programming Data File | .rpd | Stores data for configuration with third-party programming hardware. You generate Raw Programming Data Files from a .pof or .sof. The .rpd file is a subset of a .pof or .jic that includes only device-specific binary programming data for Active Serial configuration scheme with EPCS or EPCQ serial configuration devices and remote system update. |

| Tabular Text File | .ttf | A TTF contains the decimal equivalent of a Raw Binary File (.rbf). |

The options available in the Convert Programming File dialog box change dynamically, according to your device and configuration mode selection.

- Generate the primary programming files for your design, as Generating Primary Device Programming Files describes.

- Click File > Convert Programming Files.

- Under Output programming file, select the Programming file type that you want to generate. Secondary Programming Files (Convert Programming Files) describes all file options.

- Specify the File name and output directory (…) for the file that you generate.

- For the configuration Mode, select Active Serial x4 or Active Serial. Configuration Modes (Convert Programming Files) describes all modes.Note: Intel® Stratix® 10 devices support only Active Serial x4.

- To specify the Configuration device, click the (…) button to select a supported flash memory device and predefined programming flow. When you select a predefined device, you cannot modify any setting. Alternatively, click <<new device>> to define a new flash memory device and programming flow. Configuration Device Tab Settings describes all settings.Figure 7. Configuration Device Dialog Box

- Under Input files to convert, select the SOF Data item, and then click the Add File button. Specify the .sof file that contains the configuration bitstream data. To include raw data, click Add Hex Data and specify a .hex file.

- To enable bitstream compression or encryption security settings, select the .sof file and click Properties, as Enabling Bitstream Encryption or Compression for Intel Arria 10 and Intel Cyclone 10 GX Devices describes.

- Select the Flash Loader text, and then click the Add Device button. Select the device that controls loading of the flash device.Figure 8. Selecting the Flash Loader Device

- After you specify all options in the Convert Programming File dialog box, click the Generate button to create the files.

| Programming File Type | Extension | Description |

|---|---|---|

| CvP Files | .jic/.rbf | Files required for CvP configuration. |

| Hexadecimal ( Intel®-Format) Output File for SRAM | .hexout | An ASCII text file in Intel® hexadecimal format that contains configuration data for programming a parallel data source, such as a configuration device or a mass storage device. The parallel data source in turn configures an SRAM-based Intel device. |

| JTAG Indirect Configuration File | .jic | Proprietary Intel® FPGA file type that stores serial flash programming data for programming via Intel® FPGA JTAG pins. This method only supports Active Serial configuration. Before programming the flash, the Programmer first configures the FPGA with the Serial Flash Helper Design. |

| Memory Map File | .map | Contains the byte addresses of pages and HEX data stored in the memory of an EPC4, EPC8, or EPC16 configuration device. The MAP File stores the start and end addresses of the Main Block Data and Bottom Boot Data items, and the start and end addresses of pages within the Main Block Data item. |

| Partial-Masked SRAM Object Files | .pmsf | Contains the partial-mask bits for configuration of a PR region. The .pmsf file contains all the information for creating PR bitstreams. |

| Merged Mask Setting File | .msf | Contains the mask bits for the static region in a PR design. |

| Programmer Object File | .pof | A binary file that contains the data for programming non-volatile Intel® MAX® 10, MAX® V, MAX® II, or flash memory devices that can configure Intel FPGA devices. A Programmer consists of a remote update enabled .pof and additional remote update enabled .sof that you used to program configuration devices in remote update configuration mode. |

| Raw Binary File | .rbf | Configuration bitstream file for use with a third-party data source, partial reconfiguration, or HPS data source. Supports Passive Serial (PS) and Avalon®-Streaming (AVST) modes. |

| Raw Programming Data File | .rpd | Stores data for configuration with third-party programming hardware. You generate Raw Programming Data Files from a .pof or .sof. The .rpd file is a subset of a .pof or .sof that includes only device-specific binary programming data for Active Serial configuration scheme with EPCS or EPCQ serial configuration devices and remote system update. The .rpd file content has one bit swapped in comparison with the output file. |

| Tabular Text File | .ttf | A TTF contains the decimal equivalent of a Raw Binary File (.rbf). |

| Programming Mode | Description |

|---|---|

| 1-Bit/2-Bit/4-Bit/8-Bit Passive Serial | An external controller passes configuration data to one or more FPGA devices via a serial data stream. The FPGA device is a slave device with a 5-wire interface to the external controller. The external controller can be an intelligent host such as a microcontroller or CPU, or the Intel® Quartus® Prime Programmer, or an EPC2 or EPC16 configuration device. |

| Active Parallel | Supports configuration devices using commodity 16-bit parallel flash memories to control the configuration interface. |

| Active Serial | For storing configuration data in a low-cost serial configuration device with non-volatile memory. Serial configuration devices provide a serial interface to access the configuration data. During device configuration, the device reads the configuration data through the serial interface, decompresses the data if necessary, and configures their SRAM cells. |

| Active Serial x4 | |

| AVST x8/x16/x32 | The Avalon®-ST configuration mode uses an external host, such as a microprocessor or Intel® MAX® 10 device. The external host controls the transfer of configuration data from an external storage such as flash memory to the FPGA. The design that controls the configuration process resides in the external host. You can use the PFL II IP core with an Intel® MAX® 10 device as the host to read configuration data from a flash memory device that configures an FPGA. |

| Passive Parallel Synchronous | An external controller, such as a CPU, loads the design data into a device via a common data bus. Data is latched by the device on the first rising edge of a CPU-driven clock signal. The next eight falling clock edges serialize this latched data within the device. The device latches the next 8-bit byte of data on every eighth rising edge of the clock signal until the device is completely configured. |

| Passive Parallel Asynchronous | An external controller, such as a CPU, loads the design data into a device via a common data bus. The device accepts a parallel byte of input data. Intelligent communication between the external controller and the device allows the external controller to configure the device. |

| Internal Configuration | Uses a .pof file for internal configuration of the Intel® MAX® 10 device’s Configuration Flash Memory (CFM) and User Flash Memory (UFM) via a download cable Intel® Quartus® Prime Programmer. |

Changes in the Advanced Options dialog box affect .pof, .jic, .rpd, and .rbf file generation.

The following table describes the Advanced Options settings:

| Option Setting | Description | Values |

|---|---|---|

| Disable EPCS/EPCQ ID check | Directs the FPGA to skips the EPCS/EPCQ silicon ID verification. Applies to single and multi device AS configuration modes on all devices. | Default setting is ON (EPCS/EPCQ ID check is enabled). |

| Disable AS mode CONF_DONE error check | Directs the FPGA to skip the error check. Applies to single- and multi-device (AS) configuration modes on all devices. | Default setting is OFF (AS mode error check is enabled). |

| Program Length Count adjustment | Specifies the offset you can apply to the computed PLC of the entire bitstream. Applies to single- and multi-device (AS) configuration modes on all FPGA devices. | Integer (Default = 0) |

| Post-chain bitstream pad bytes | Specifies the number of pad bytes appended to the end of an entire bitstream. | If the bitstream of the last device is uncompressed, default value is 0. Otherwise, default is 2 |

| Post-device bitstream pad bytes | Specifies the number of pad bytes appended to the end of the bitstream of a device. Applies to all single-device configuration modes on all FPGA devices. | Zero or positive integer. Default is 0 |

| Bitslice Padding Value | Specifies the padding value used to prepare bitslice configuration bitstreams, such that all bitslice configuration chains simultaneously receive their final configuration data bit. Use only in 2, 4, and 8-bit PS configuration mode, when you use an EPC device with the decompression feature enabled. Applies to all FPGA devices that support enhanced configuration devices. | 0 or 1 Default value is 1 |

The following table lists possible symptoms of a failing configuration, and describes the advanced options necessary for configuration debugging.

| Failure Symptoms | Disable EPCS/EPCQ ID Check | Disable AS Mode CONF_DONE Error Check | PLC Settings | Post-Chain Bitstream Pad Bytes | Post-Device Bitstream Pad Bytes | Bitslice Padding Value |

|---|---|---|---|---|---|---|

| Configuration failure occurs after a configuration cycle. | — | Yes | Yes | Yes 3 | Yes 4 | — |

| Decompression feature is enabled. | — | Yes | Yes | Yes 3 | Yes 4 | — |

| Encryption feature is enabled. | — | Yes | Yes | Yes 3 | Yes 4 | — |

| stays low after a configuration cycle. | — | Yes | Yes 5 |

Zimbra Collaboration 9.0.0 Upgrade Steps

Zimbra Touch Client, Zimbra Mobile Client, and Zimbra HTML (Standard) Client are no longer a part of Zimbra starting from Version 9.0.0.

| Zimbra Connect replaces Zimbra Talk during the upgrade process. You must choose to install when prompted as is removed later during the upgrade process. |

If you are currently on Zimbra V8.8.15 Patch 7, update all NG modules before upgrading to Zimbra 9.0.0.

Zimbra 9.0.0 introduces two versions of Zimbra Web Client — Modern and Classic.

A Zimbra Network Edition license is required to use the Modern Web App.

It is recommended that the Modern Web App is set as the default web client. Even after selecting a default, the Modern Web App and the Classic Web App can be used simultaneously by users as per their choice.

To know more about highlights of the Modern Web App, please refer to Introducing the Modern Web Application.

The Classic Web App offers the same functionality as the Advanced Web Client in Zimbra version 8.8.15.

The Modern Web App is actively under development, with some features not yet available. Refer to Email Features (e.g., Personas, System Distribution Lists, and Dumpster.

Briefcase cannot be used with Modern Web App. Though users may continue to use Briefcase with Classic Web App, it is recommended that existing users of Briefcase migrate to Zimbra Drive.

Existing customized themes, logo branding changes, and crontab changes are incompatible with, and hence do not reflect in the Modern Web App. Branding needs to be re-configured to work with the Modern Web App. The Modern Web App does not currently support themes. Please refer to the Customizing Modern Web App section of Admin Guide for more information related to configuration.

Currently supported languages in the application UI for the Modern Web App are - Chinese (China), English (US), French (France), German, Hindi, Indonesian, Italian, Japanese, Portuguese (Portugal), Spanish and Thai.

Zimlets are supported on both the Web Clients.

Zimlets that work with Zimbra 8.8 will work with the Classic Web App; however, they are incompatible with the Modern Web App. Due to technology changes, there is no way to migrate the Zimlets from the Classic Web App to the Modern Web App or vice-versa.

The Zimlets for Zimbra Drive, Zimbra Connect and Zimbra Docs are available for both web applications.

What’s New in the Map & Guide v9.0 German serial key or number?

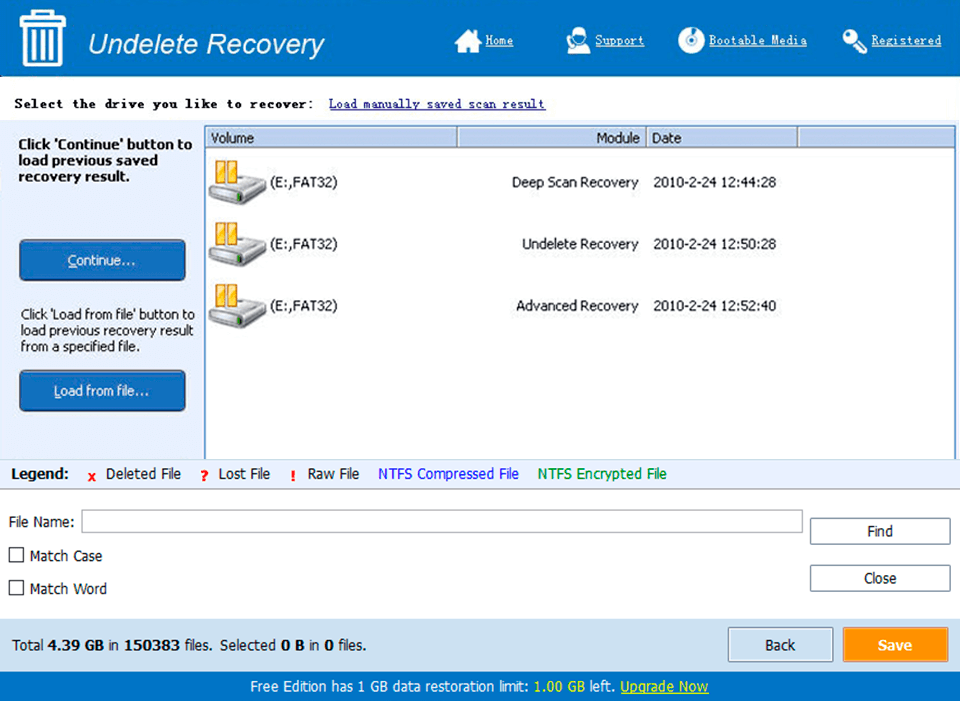

Screen Shot

System Requirements for Map & Guide v9.0 German serial key or number

- First, download the Map & Guide v9.0 German serial key or number

-

You can download its setup from given links: