ExplorerView 4.4.2 keygen

ExplorerView 4.4.2 keygen

eSDK TP 1.1.RC3.SPC003 Development Guide 01 (Server, SOAP)

|

| ||

| |||

| eSDK TP 1.1.RC3.SPC003 Development Guide (Server, SOAP) | ||

| |||

Issue | 01 | ||

Date | 2018-03-19 | ||

HUAWEI TECHNOLOGIES CO., LTD. | |||

Copyright © Huawei Technologies Co., Ltd. 2018. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written consent of Huawei Technologies Co., Ltd.

Trademarks and Permissions

All other trademarks and trade names mentioned in this document are the property of their respective holders.

Notice The purchased products, services and features are stipulated by the contract made between Huawei and the customer. All or part of the products, services and features described in this document may not be within the purchase scope or the usage scope. Unless otherwise specified in the contract, all statements, information, and recommendations in this document are provided "AS IS" without warranties, guarantees or representations of any kind, either express or implied. The information in this document is subject to change without notice. Every effort has been made in the preparation of this document to ensure accuracy of the contents, but all statements, information, and recommendations in this document do not constitute a warranty of any kind, express or implied. |

Huawei Technologies Co., Ltd. | |

Address: | Huawei Industrial Base Bantian, Longgang Shenzhen 518129 People's Republic of China |

Website: | http://e.huawei.com |

Huawei eSDK TP(Telepresence) for SOAP is developed based on the service management platform (SMC2.0) of Huawei videoconferencing solution. It is based on standard SOAP APIs and provides unified account management, video conference scheduling, and conference control capabilities for partners.

Its rich open capabilities allow partners to integrate Huawei videoconferencing solution with upper-level industry applications and to develop secure, convenient, and practical video conference scheduling platforms for customers in the government, transportation, and education sectors and other high-end enterprise customers.

What Are Provided by eSDK TP for SOAP

SOAP API

SOAP API used for video conference secondary development. It contains WSDL files and the interface reference.

Sample code

Sample code provided by the Huawei SDK to demonstrate how to invoke interfaces, helping developers develop video conference services. For details, see 3.3 Sample Code.

IDE support

eSDK IDE plug-in based on Visual Studio or Eclipse that provides functions such as demo download and installation, remote lab access, and online technical support, offering better experience for developers. The IDE can help developers create, configure, and commission projects, simplifying the secondary development process. For details, see 3.5 IDE Plug-in.

GitHub source code

Source code for the Huawei eSDK TP secondary development in multiple languages. For more code resources, visit GitHub.

About SMC2.0

The SMC2.0 provides Huawei videoconferencing device management and service control functions, and supports hierarchical and role-based management based on the enterprise architecture.

Using the SMC2.0, the system administrator can manage and maintain network-wide devices in a unified manner. Common users can use the rich conference initiation and control functions provided by the SMC2.0 to enjoy the communication joy brought by video conferences.

For details, visit the SMC2.0 page.

What Is in the Development Guide

This document provides guidance for developers to install and configure the environment, use the SOAP API to invoke service functions of the SMC2.0, and obtain technical support provided by the Huawei eSDK. This document consists of the following parts:

1. 3 Related Resources: Software, document resource website links, and technical support that may be involved in secondary development, including how to obtain materials from Huawei Developer Zone, download link of sample code, IDE plug-in introduction and usage, and how to apply for the remote lab.

2. 4 Hello World: Quick start guide to run the SDK. You should first read this chapter to learn how to download and deploy the WSDL and configure the development environment.

3. 5 Initial Configuration: Initial configuration that needs to be performed before you develop service functions. You need to perform the initial configuration only once.

4. 6 Typical Development Scenarios: Typical development scenarios of the eSDK TP, consisting of development process, sample code, and precautions.

5. 7 Fault Locating Guide: Methods of locating common development problems.

6. 8 Change History: Update details of each development guide version.

Reading Guidance

l For a quick start, read 4 Hello World.

l To thoroughly understand secondary development of the core eSDK TP services, read 6 Typical Development Scenarios.

l If you encounter any problems when you use the SDK, refer to 7 Fault Locating Guide to locate the problem, search for related information in online FAQs, or contact eSDK TP technical support.

This document is used with SDK 1.1.RC3.SPC003.

3.1 Huawei Developer Zone

Visit the Telepresence & Videoconferencing page of Huawei Developer Zone to experience video conference service functions or obtain SDK tool packages or technical support for eSDK TP secondary development.

3.2 Software Packages Download Path

Download the eSDK platform installation package and eSDK TP service package of the corresponding version by clicking the links:

l eSDK platform installation package:

− Windows operating system (64-bit): eSDK_Platform_V2.1.20.201_Windows_x64.zip

− Linux operating system: eSDK_Platform_V2.1.20.201_SLES_x64.zip

l eSDK TP service package: eSDK_TP_1.1.RC3.SPC003.zip

3.3 Sample Code

You are advised to use Eclipse 4.4 or higher to compile or execute the sample code.

The sample code list contains the source code paths of sample code described in 6 Typical Development Scenarios. Sample code demonstrates how to invoke eSDK TP interfaces.

The following provides the sample code list.

eSDK_TP_SOAP_Demo_BS_Java | Typical scenario demo developed based on TP SOAP interfaces, including the functions for accessing the videoconferencing system, initiating a video conference consisting of two or more sites, scheduling a conference using a conference template (ad hoc conference scenario), and controlling a video conference. |

eSDK_TP_Demo_CS_Java | TP C/S demo developed based on TP SOAP interfaces in Java. |

eSDK_TP_Demo_BS_Java | TP B/S demo developed based on TP SOAP interfaces in Java. |

If you want to know how to download and deploy the WSDL, see 4 Hello World.

3.4 Interface Reference

This document is used with the eSDK TP 1.1.RC3.SPC001 Interface Reference 01 (Server, SOAP), which contains the following content:

Overview: mapping versions, usage background, scenarios, prerequisites, information that can be obtained, and functions to be performed.

Data types: description of customized data types (including classes, structures, and enumerations) provided by the eSDK, including:

l Data type names

l Description of data structures that involve inheritance and nesting, such as structure nesting relationships (a total nesting table including basic data types must be provided)

l Data members and their definitions

Interface description:

l Interface description: description of interface function, application scenarios, and usage.

l Usage description: precautions for using the interface function, usage limitation, interfaces with similar functions, associated interfaces, and prerequisites.

l

E-tile Hard IP Intel Stratix 10 Design Examples User Guide: Ethernet, CPRI PHY, and Dynamic Reconfiguration

| Updated for: |

|---|

| Intel® Quartus® Prime Design Suite 20.2 |

The E-tile Hard IP for Ethernet Intel® FPGA IP core for Intel® Stratix® 10 devices provides a simulation testbench and a hardware design example that supports compilation and hardware testing. When you generate the design example, the parameter editor automatically creates the files necessary to simulate, compile, and test the design in hardware.

In addition, you can download the compiled hardware design to the Intel® Stratix® 10 TX Transceiver Signal Integrity Development Kit. Intel® provides a compilation-only example project that you can use to quickly estimate IP core area and timing.

| Data Rate | Variant | Simulation | Compilation-Only Project | Hardware Design Example |

|---|---|---|---|---|

| 10GE | Single or multi channels Media Access Controller (MAC) + Physical Coding Sublayer (PCS) with optional 1588 Precision Time Protocol (PTP) | √ | √ | √ |

| Single channel PCS | √ | √ | √ | |

| Single channel Optical Transport Network (OTN) | √ | √ | X | |

| Single channel Flexible Ethernet (FlexE) | √ | √ | X | |

| Single or multi channels custom PCS | √ | √ | √ | |

| 25GE | Single or multi channels MAC + PCS with optional RS-FEC and optional PTP

| √ | √ | √ |

| Single channel PCS with optional RS-FEC | √ | √ | √ | |

| Single channel OTN with optional RS-FEC | √ | √ | X | |

| Single channel FlexE with optional RS-FEC | √ | √ | X | |

| Single or multi channels custom PCS with optional RS-FEC | √ | √ | √ | |

| 100GE | MAC+ PCS with optional: | √ | √ | √ |

| MAC+PCS with (544, 514) RS-FEC | √ | √ | √ | |

| PCS with optional (528,514) or (544, 514) RS-FEC | √ | √ | √ | |

| OTN with optional (528,514) or (544, 514) RS-FEC | √ | √ | X | |

| FlexE with optional (528,514) or (544, 514) RS-FEC | √ | √ | X |

The E-Tile Hard IP for Ethernet Intel FPGA IP design example file directories contain the following generated files for the design examples.

File Names | Description |

|---|---|

| Key Testbench and Simulation Files | |

| <design_example_dir>/example_testbench/basic_avl_tb_top.sv | Top-level testbench file. The testbench instantiates the DUT and runs Verilog HDL tasks to generate and accept packets. |

| Testbench Scripts | |

| <design_example_dir>/example_testbench/run_vsim.do | The Mentor Graphics ModelSim* script to run the testbench. |

| <design_example_dir>/example_testbench/run_vcs.sh | The Synopsys VCS* script to run the testbench. |

| <design_example_dir>/example_testbench/run_vcsmx.sh | The Synopsys VCS MX* script (combined Verilog HDL and System Verilog with VHDL) to run the testbench. |

| <design_example_dir>/example_testbench/run_ncsim.sh | The Cadence NCSim* script to run the testbench. |

| <design_example_dir>/example_testbench/run_xcelium.sh | The Xcelium* script to run the testbench. |

File Names | Description |

|---|---|

| <design_example_dir>/hardware_test_design/alt_ehipc3_hw.qpf | Intel® Quartus® Prime project file. |

| <design_example_dir>/hardware_test_design/alt_ehipc3_hw.qsf | Intel® Quartus® Prime project settings file. |

| <design_example_dir>/hardware_test_design/alt_ehipc3_hw.sdc | Synopsys Design Constraints files. You can copy and modify these files for your own Intel® Stratix® 10 design. |

| <design_example_dir>/hardware_test_design/alt_ehipc3_hw.v | Top-level Verilog HDL design example file. |

| <design_example_dir>/hardware_test_design/common/ | Hardware design example support files. |

| hwtest_sl/main_script.tcl (10GE/25GE) hwtest/main.tcl (100GE) | Main file for accessing System Console. |

- In the Intel® Quartus® Prime Pro Edition software, click File > New Project Wizard to create a new Quartus Prime project, or File > Open Project to open an existing Intel® Quartus® Prime project. The wizard prompts you to specify a device.

- Specify the device family Intel® Stratix® 10 and select a device that meets all of these requirements:

- Transceiver tile is E-tile

- Transceiver speed grade is -1, -2 or -3

- Core speed grade is -1 or -2

- Click Finish.

- In the IP Catalog, locate and select E-Tile Hard IP for Ethernet Intel FPGA IP. The New IP Variation window appears.

- Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation settings in a file named .ip.

- Click OK. The parameter editor appears.

- On the IP, 100GE, or 10GE/25GE tabs, specify the parameters for your IP core variation.

- The hardware design examples provide enable internal serial loopback by default.

- Change PMA adaptation setting. To change the PMA adaptation setting for the optimal performance, go to PMA Adaptation tab. This step is optional.

- Select a PMA adaptation preset for PMA adaptation Select parameter.

- Click PMA Adaptation Preload to load the initial and continuous adaptation parameters.

- Specify the number of PMA configurations to support when multiple PMA configurations are enabled using Number of PMA configuration parameter.

- Select which PMA configuration to load or store using Select a PMA configuration to load or store.

- Click Load adaptation from selected PMA configuration to load the selected PMA configuration settings.

For more information about the PMA adaptation parameters, refer to the E-Tile Transceiver PHY User Guide.

Note: If you require more information about the PMA adaptation parameters, contact My Intel support. - On the Example Design tab, under Example Design Files, select the Simulation option to generate the testbench and the compilation-only project. Select the Synthesis option to generate the hardware design example. You must select at least one of the Simulation and Synthesis options to generate the design example.

- On the Example Design tab, under Generated HDL Format, select Verilog HDL or VHDL. If you select VHDL, you must simulate the testbench with a mixed-language simulator. The device under test in the ex_<datarate> directory is a VHDL model, but the main testbench file is a System Verilog file.

- Under Target Development Kit, select the Stratix 10 TX Transceiver Signal Integrity Development Kit-1ST280EY2F55E2VGSI, Stratix 10 TX Transceiver Signal Integrity Development Kit-1ST280EY2F55E2VG or select None. If you select a specific Development Kit as the Target Development Kit, the design example is generated based on a specific device and it overwrites the device you selected in your project file. If you select None as the Target Development Kit, ensure the selected device is your targeted device and adjust the pins assignment in the file. By default, file is generated based on the device used in the development kit

- Click the Generate Example Design button. The Select Example Design Directory window appears.

- If you want to modify the design example directory path or name from the defaults displayed (alt_ehipc3_0_example_design), browse to the new path and type the new design example directory name ().

Follow these steps to simulate the testbench:

- Change to the testbench simulation directory /example_testbench.

- Run the simulation script for the supported simulator of your choice. The script compiles and runs the testbench in the simulator. Refer to the table Steps to Simulate the Testbench.

- Analyze the results. The successful testbench sends ten or fourteen packets, receives the same number of packets, and displays

Simulator Instructions Mentor Graphics ModelSim* * In the command line, type vsim -do run_vsim.do If you prefer to simulate without bringing up the ModelSim GUI, type vsim -c -do run_vsim.do

Note: The ModelSim* - Intel® FPGA Edition simulator does not have the capacity to simulate this IP core. You must use another supported ModelSim simulator such as ModelSim* SE.Cadence NCSim* In the command line, type sh run_ncsim.sh Synopsys VCS*/VCS MX* In the command line, type sh run_vcs.sh or sh run_vcsmx.sh Note:run_vcs.sh is only available if you select Verilog as the Generated HDL Format. If you select VHDL as the Generated HDL Format, you must simulate the testbench with a mixed language simulator using run_vcsmx.sh.Xcelium* In the command line, type sh run_xcelium.sh

To compile the compilation-only example project, follow these steps:

- Ensure compilation design example generation is complete.

- In the Intel® Quartus® Prime Pro Edition software, open the Intel® Quartus® Prime Pro Edition project /compilation_test_design/alt_ehipc3.qpf.

- On the Processing menu, click Start Compilation.

After successful compilation, reports for timing and for resource utilization are available in your Intel® Quartus® Prime Pro Edition session.

To compile the hardware design example and configure it on your Intel® Stratix® 10 device, follow these steps:

- Ensure hardware design example generation is complete.

- In the Intel® Quartus® Prime Pro Edition software, open the Intel® Quartus® Prime project /hardware_test_design/alt_ehip3.qpf.

- On the Processing menu, click Start Compilation.

- After successful compilation, a .sof file is available in /hardware_test_design/output_files directory. Follow these steps to program the hardware design example on the Intel® Stratix® 10 device:

- Connect Stratix 10 E-Tile TX Transceiver Signal Integrity Development Kit to the host computer.

- Launch the Clock Control application, which is part of the development kit, and set new frequencies for the design example. Below is the frequency setting in the Clock Control application:

- Y1—Set to the PHY Reference Frequency specified in the PMA adaptation setting of your IP core variation.

For 10GE/25GE variant, select 10GE/25GE tab and locate the PMA Options 10GE/25GE setting.

For 100GE variant, select 100GE tab and locate the PMA Options 100GE setting.

- U3, OUT3—100 MHz

- Y1—Set to the PHY Reference Frequency specified in the PMA adaptation setting of your IP core variation.

- On the Tools menu, click Programmer.

- In the Programmer, click Hardware Setup.

- Select a programming device.

- Select and add the Stratix 10 E-Tile TX Transceiver Signal Integrity Development Kit to which your Intel® Quartus® Prime Pro Edition session can connect.

- Ensure that Mode is set to JTAG.

- Select the Intel® Stratix® 10 device and click Add Device. The Programmer displays a block diagram of the connections between the devices on your board.

- In the row with your .sof, check the box for the .sof.

- Check the box in the Program/Configure column.

- Click Start.

After you compile the E-Tile Hard IP for Ethernet Intel FPGA IP core design example and configure it on your Intel® Stratix® 10 device, you can use the System Console to program the IP core and its embedded Native PHY IP core registers.

To turn on the System Console and test the hardware design example, follow these steps:

- After the hardware design example is configured on the Intel® Stratix® 10 device, in the Intel® Quartus® Prime Pro Edition software, on the Tools menu, click In-System Sources and Probes Editor.

- In the JTAG Chain Configuration window, select the USB connection that is connected to the development kit.

- Next, from the Device list, select the device with string in the name. The Ready to acquire status appears at the bottom of the Instance Manager window if the correct device is selected.

- A list of instances appears once the connection is acquired. There are four sources under index 0. These sources have the following connections:

Source Signal source[3] (active low) source[2] (active low) source[1] (active low) source[0] (active high) - Toggle source[0] to initiate reset for the transceiver and Ethernet reconfiguration interfaces.

- Once the reset is initiated, on the Tools menu, click System Debugging Tools > System Console.

- In the Tcl Console pane, type to change directory to <>/hardware_test_design/hwtest_sl.

- Type to configure the test according to your design configuration:

Command Setting Description Set this value according to the value of Number of Channels of 10GE/25GE parameter in your design. The default value is 1. Example, in the system console type to change the number of channels to 2.

Note:E-Tile Hard IP for Ethernet Intel FPGA IP does not support multichannel PCS variation.Set this value to the JTAG port ID that is connected to the development kit. Example, in the system console type to change the JTAG ID to 0.

Set this to 1 to enable Internal Serial Loopback. The default value is 1. Example, in the system console, type to disable Internal Serial Loopback.

Set this to 1 if PTP is enabled in the design. Otherwise set the value to 0. The default value is 0. Example, in the system console type to enable PTP.

Choose the following option according to the design example variation: - for 10 Gbps data rate

- for 25 Gbps data rate

- for 25 Gbps data rate with RS-FEC enabled

- for PCS only and custom PCS designs

- for PCS only and custom PCS designs with RS-FEC enabled

Example, in the system console type to set the data rate to 25G with RS-FEC enabled.

Set this to 1 if Enable adaptation load soft IP parameter is enabled in your design. Otherwise, set the value to 0. The default value is 0. Set the PMA configuration number to enable PMA adaptation. The PMA configuration number set must be one of the PMA configurations defined in your design. - Type to enable the internal loopback and run the test.

Set the speed to to configure 10GE/25GE PCS only with optional RS-FEC hardware test. Set the speed to to configure 10G/25G custom PCS with optional RS-FEC hardware test.

This hardware design example enables internal serial loopback mode by default. To run the hardware design with external loopback mode, select Enable adaptation load soft IP in the parameter editor before generating the design example.

To turn on the System Console and test the hardware design example, follow these steps:

- After the hardware design example is configured on the Intel® Stratix® 10 device, in the Intel® Quartus® Prime Pro Edition software, on the Tools menu, click System Debugging Tools > System Console.

- In the Tcl Console pane, type to change directory to <>/hardware_test_design/hwtest.

- Type to open a connection to the JTAG master.

You can use the following design example commands to configure the 100GE hardware design example test with internal serial loopback mode. For example, in the system console, type and press .

- 1/2: To run hardware design example tests.

- 1/2: To perform PMA adaptation.

- : Displays the clock frequencies and PHY lock status.

- : Displays the values in the MAC statistics counters.

- : Clears the IP core statistics counters.

- : Starts the packet generator.

- : Stops the packet generator.

- 1/2: Turns on internal serial loopback.

- : Turns off internal serial loopback.

- : Returns the IP core register value at <>. Example, to read TX datapath PCS ready register, type .

- : Writes <> to the IP core register at address <>. Example, to initiate soft reset on RX PCS, type

- 1/2: Check for PAM4 PMA adaptation status.

- Optional step: To run the MAC+PCS with (528,514) RS-FEC or (544, 514) RS-FEC and PMA adaptation design example in external loopback mode, open hardware_test_design/hwtest/main.tcl file and uncomment 1/2 command.

Make sure the Enable adaptation load soft IP is selected and the PMA adaptation Select is set to:

Embedded Design Handbook

The Embedded Design Handbook complements the primary documentation for the Intel tools for embedded system development. It describes how to most effectively use the tools, and recommends design styles and practices for developing, debugging, and optimizing embedded systems using Intel-provided tools. The handbook introduces concepts to new users of Intel’s embedded solutions, and helps to increase the design efficiency of the experienced user.

| Document Version | Changes |

|---|---|

| 2020.07.22 | Updated the following chapters:

|

| 2020.04.25 | Updated the Software System Design with a Nios® II Processor chapter. |

| 2020.01.13 | Updated the Software System Design with a Nios® II Processor chapter. |

| 2018.11.12 | Updated the following chapters:

|

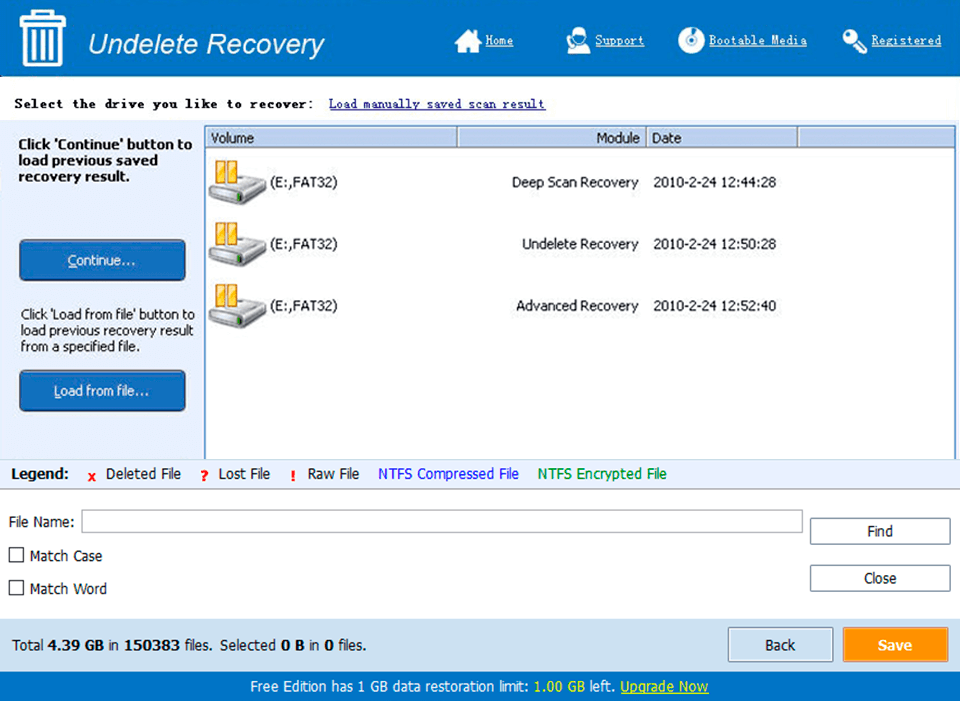

What’s New in the ExplorerView 4.4.2 keygen?

Screen Shot

System Requirements for ExplorerView 4.4.2 keygen

- First, download the ExplorerView 4.4.2 keygen

-

You can download its setup from given links: